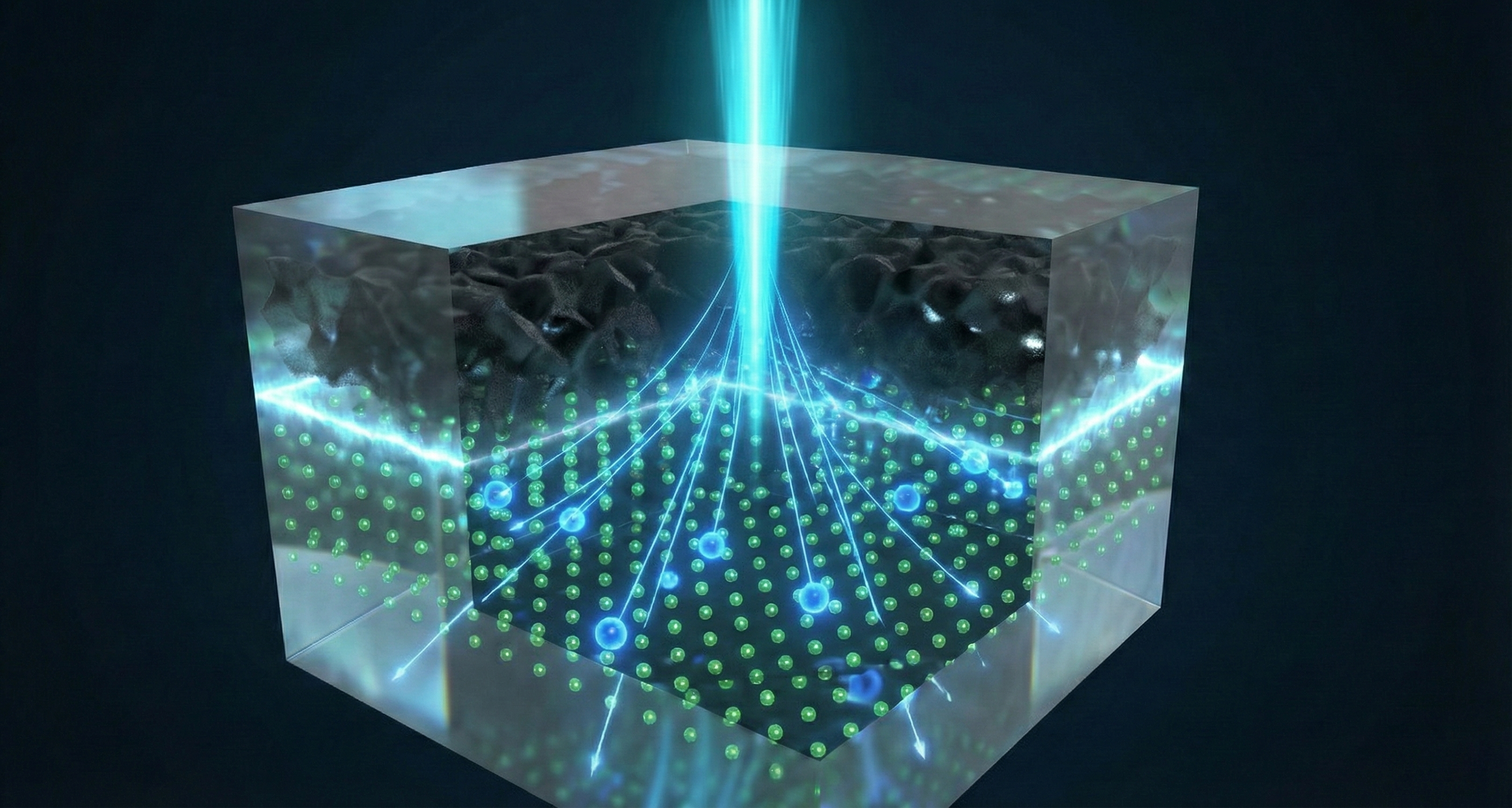

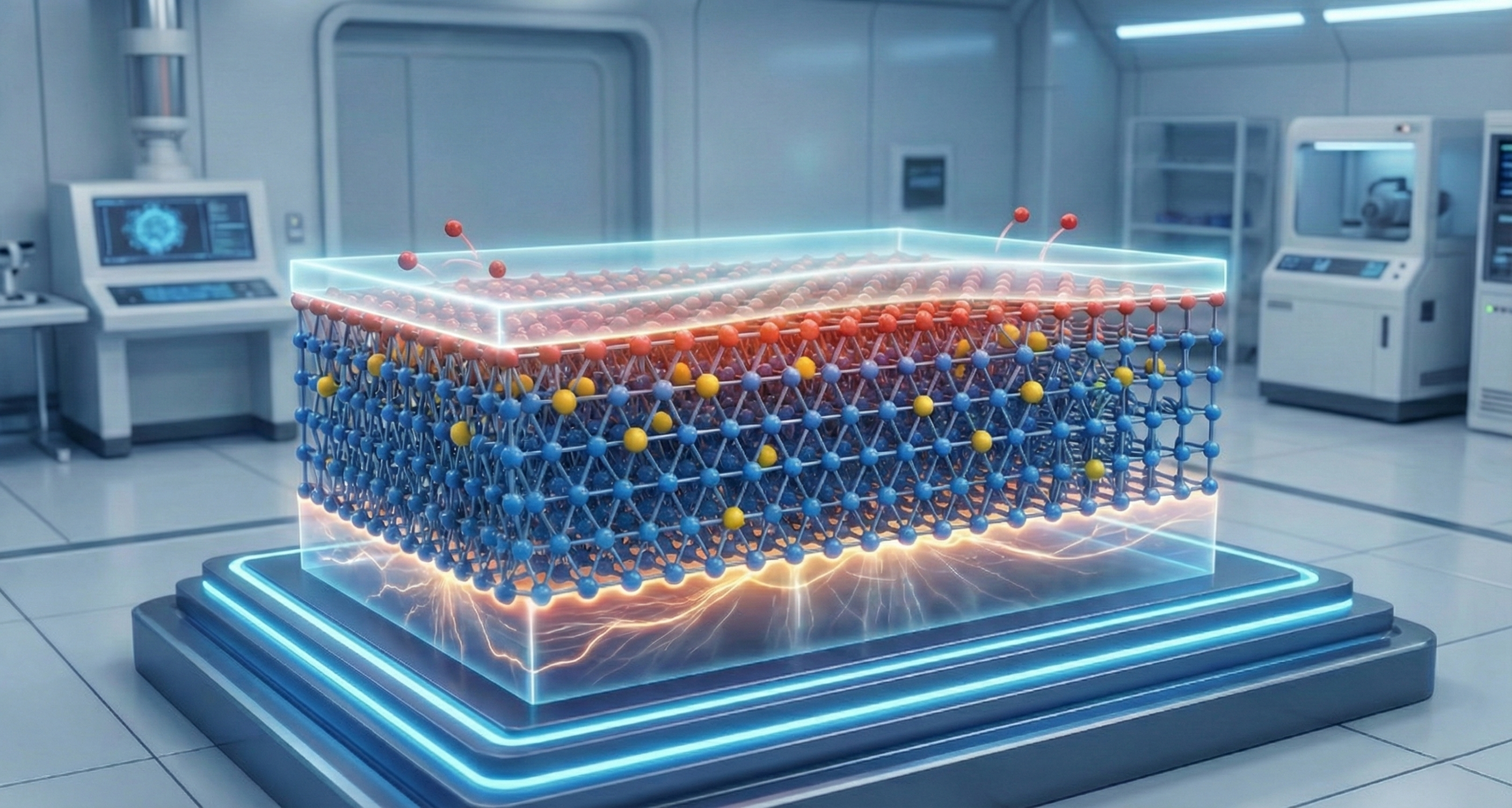

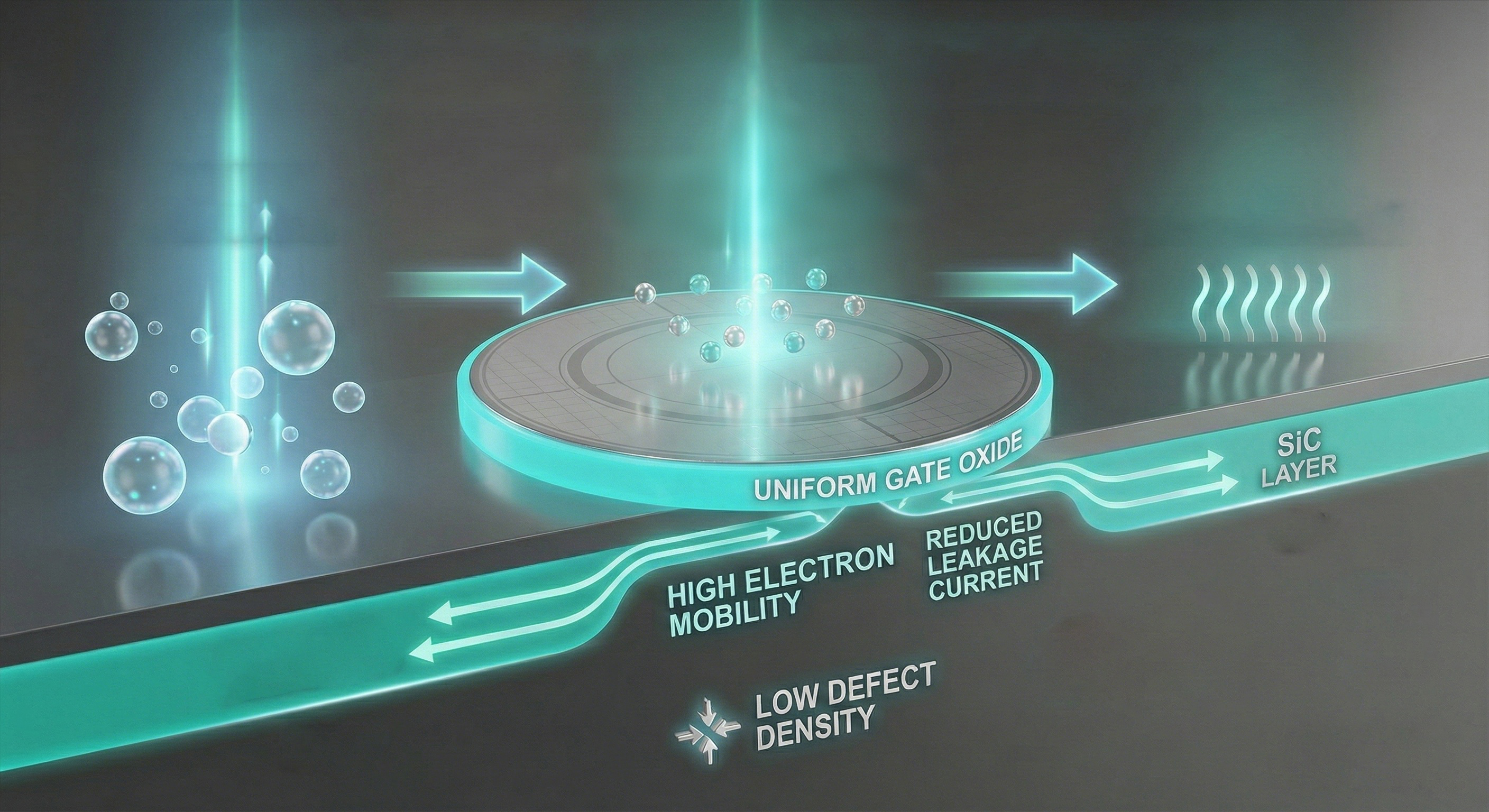

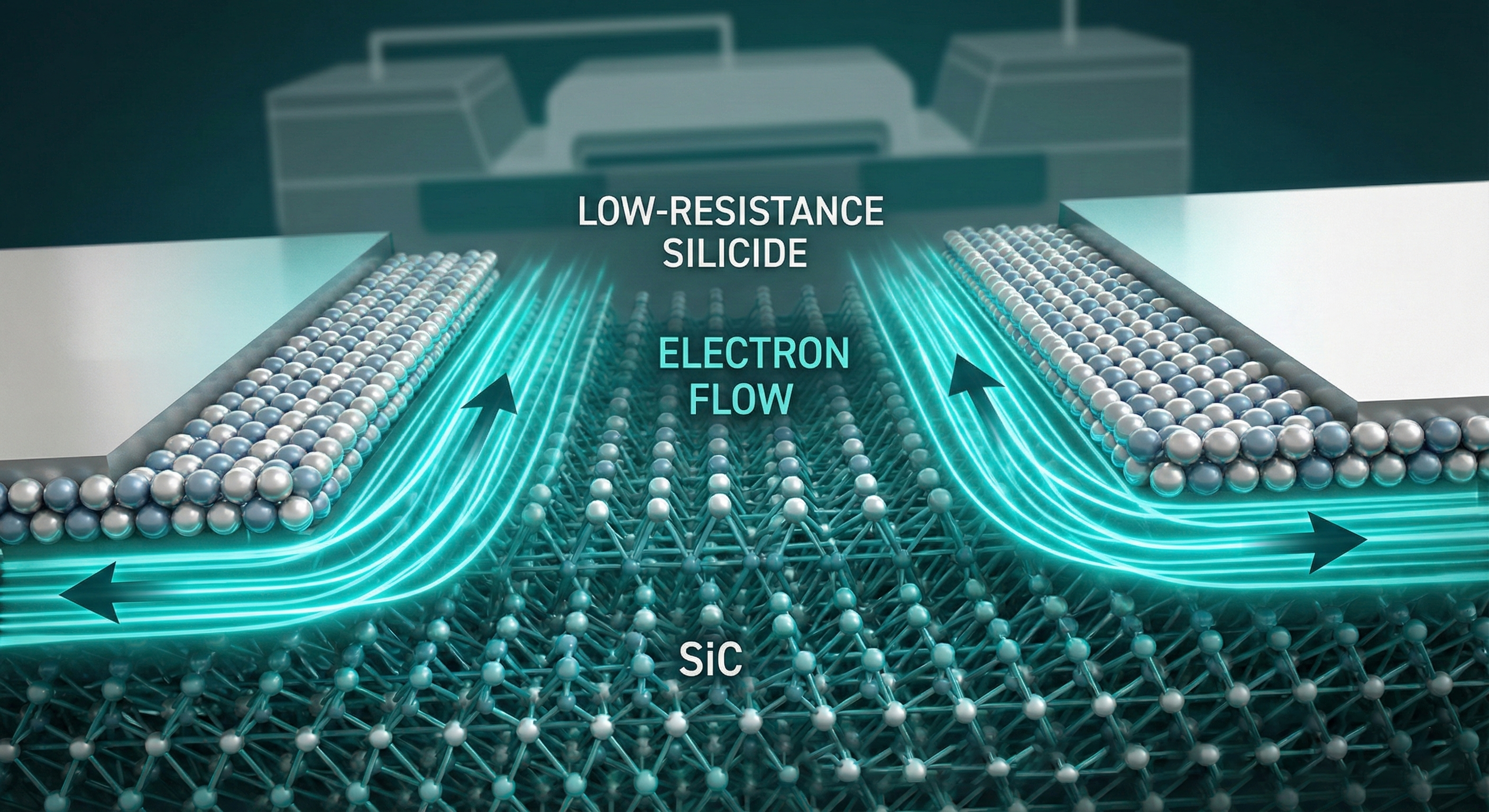

Deep Ion Implantation Technology

Advanced high-energy, high-current, and high-temperature deep ion implantation technology enables precise control of doping depth and concentration profiles, forming optimized doping structures in target regions. Through lattice damage suppression and activation mechanisms, the technology significantly reduces device on-resistance, ensuring device performance and consistency.